# Compilers

• The information needed to manage one procedure activation is called an *activation record (AR)* or *frame*

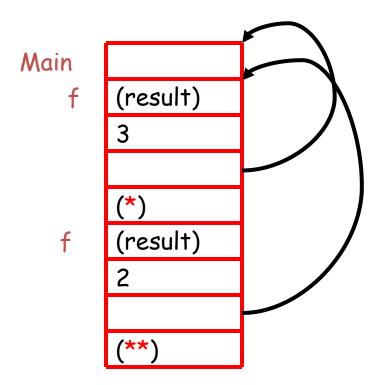

• If procedure F calls G, then G's activation record contains a mix of info about F and G.

F is "suspended" until G completes, at which point F resumes

- G's AR contains information needed to

- Complete execution of G

- Resume execution of F

- Space for G's return value

- Actual parameters

- Pointer to the previous activation record

- The control link; points to AR of caller of G

- Machine status prior to calling G

- Contents of registers & program counter

- Local variables

- Other temporary values

```

Class Main {

g(): Int { 1 };

f(x:Int):Int \{if x=0 then g() else f(x - 1)(**)fi\};

main(): Int {{f(3); (*)

}};}

result

argument

control link

AR for f:

return address

```

- Main has no argument or local variables and its result is never used; its AR is uninteresting

- (\*) and (\*\*) are return addresses of the invocations of f

- The return address is where execution resumes after a procedure call finishes

- This is only one of many possible AR designs

- Would also work for C, Pascal, FORTRAN, etc.

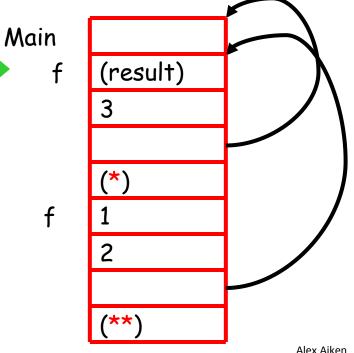

The picture shows the state after the call to the 2nd

invocation of f returns

The advantage of placing the return value 1st in a frame is that the caller can find it at a fixed offset from its own frame

- There is nothing magic about this organization

- Can rearrange order of frame elements

- Can divide caller/callee responsibilities differently

- An organization is better if it improves execution speed or simplifies code generation

- Real compilers hold as much of the frame as possible in registers

- Especially the method result and arguments

The compiler must determine, at compile-time, the layout of activation records and generate code that correctly accesses locations in the activation record

Thus, the AR layout and the code generator must be designed together!